数据库系统的三级模式与两级映像:数据独立性的基石

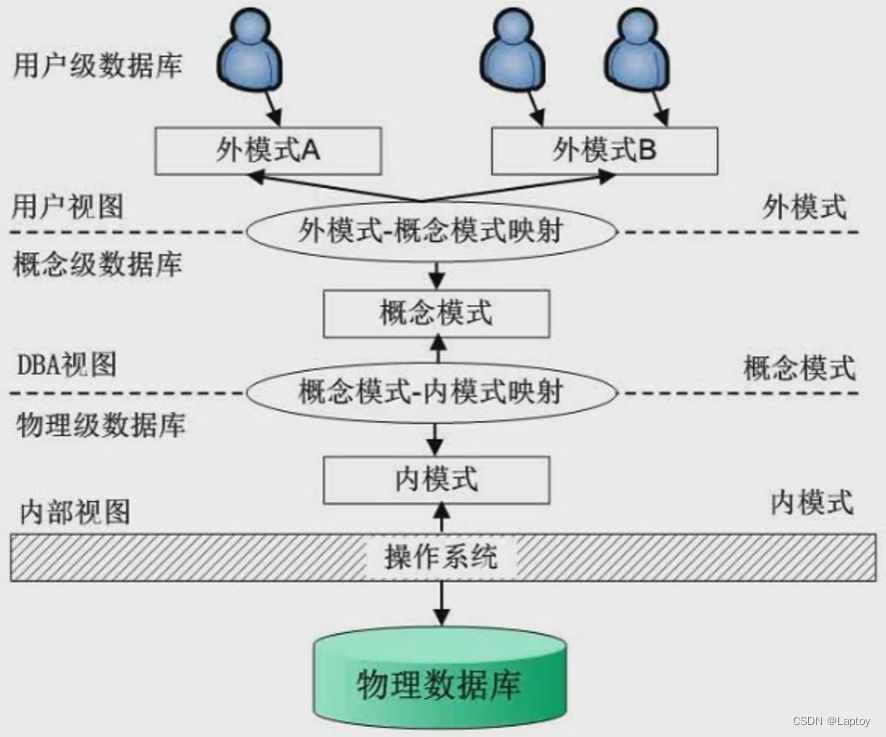

数据库系统的三级模式(外模式、概念模式、内模式)和两级映像(模式 / 内模式映像、外模式 / 模式映像)是实现数据独立性的核心架构,也是关系型数据库保持灵活性和稳定性的关键设计。这一体系结构将数据的抽象层次分离,使得用户操作、逻辑结构和物理存储可以独立演化。

三级模式结构:数据的三个抽象层次

三级模式从抽象到具体,分别对应用户视角、系统逻辑视角和物理存储视角,每一层都有明确的职责和描述对象。

外模式(External Schema):用户眼中的数据

- 定义:又称 “用户模式” 或 “子模式”,是特定用户或应用程序所能看到和使用的数据结构描述。它是概念模式的子集,只包含用户关心的部分数据。

- 特点:

- 一个数据库可以有多个外模式(不同用户 / 应用可能需要不同的数据视图)。

- 外模式屏蔽了无关数据,简化了用户操作,同时保障数据安全(用户只能访问被授权的外模式)。

- 对应数据库对象:视图(View)。视图是外模式的具体实现,用户通过视图操作数据,无需关注底层表结构。

- 描述语言:外模式 DDL(数据定义语言),用于定义用户视图的结构。