计算机存储系统:层次架构与工作原理

存储系统是计算机硬件的核心组成部分,负责数据与指令的暂存和持久化存储。现代计算机通过层次化存储结构平衡速度、容量与成本的矛盾,其设计思想贯穿了 “局部性原理” 的核心逻辑,在硬件实现与数据调度上形成了精密的协同机制。

层次化存储结构:速度与容量的平衡艺术

计算机存储系统从上到下呈现出速度递减、容量递增、成本递减的显著特征,这种架构设计基于 “高频数据近 CPU 存储” 的优化原则,具体层级如下:

1 | ^ CPU寄存器 → 速度最快(纳秒级),容量最小(bit级) |

关键存储体系组合

- 虚拟存储器:由内存与外存协同构成,通过操作系统的内存管理机制,为程序提供远超实际物理内存的 “逻辑地址空间”,解决大程序运行的内存瓶颈。

- 三级存储体系:Cache + 内存 + 外存的组合,覆盖从高频临时访问到持久化存储的全场景,通过硬件与软件的协同调度实现高效数据流转。

支撑理论:局部性原理

层次化存储结构的有效性源于程序运行的局部性特征,即:

- 时间局部性:最近被访问的数据,在短期内会被再次访问(如循环变量、反复调用的函数)。

- 空间局部性:被访问数据的临近区域,在短期内会被集中访问(如数组遍历、连续指令执行)。

这一原理使得 “将高频访问数据放到高层存储” 的策略能显著提升系统性能 —— 据统计,合理设计的三级存储体系可使 CPU 访问数据的平均延迟降低 90% 以上。

存储介质的存取方式与工作特性

不同存储介质因硬件结构差异,形成了多样化的存取方式和工作特性,直接影响其在层次结构中的定位。

按存取方式分类

- 按内容存取

- 代表:相联存储器(如 Cache)

- 原理:通过数据内容而非地址定位存储位置,支持并行查找,适用于高速缓存的地址映射。

- 按地址存取

- 随机存取存储器(RAM):如内存,可直接访问任意地址单元,读写速度一致。

- 顺序存取存储器:如磁带,数据按线性顺序存储,访问需从头至尾遍历,速度最慢。

- 直接存取存储器:如磁盘,结合随机与顺序存取特点 —— 先通过磁头定位磁道(随机),再沿磁道顺序查找扇区(顺序)。

按工作方式分类

随机存取存储器(RAM)

特性:掉电后数据丢失,用于临时存储运行中的数据。

类型对比:

| 类型 | 集成度 | 功耗 | 刷新需求 | 应用场景 |

| —— | ——————— | —— | ———————————- | ——————————- |

| DRAM | 高(单管存储) | 高 | 需要动态刷新(每 64ms) | 主流内存(DDR4/DDR5) |

| SRAM | 低(六管存储) | 低 | 无需刷新 | Cache、CPU 寄存器 |

只读存储器(ROM)

- 特性:掉电后数据保留,用于存储固定程序与配置。

- 常见类型:

- BIOS 芯片:存储计算机启动引导程序,开机时首先运行。

- EEPROM:电可擦除,以字节为单位修改数据,常用于存储硬件配置信息。

- 闪存(Flash):EEPROM 的变种,按区块擦除数据,速度更快,广泛用于 U 盘、SSD、手机存储。

内存:主存的核心功能与构成

内存(主存储器)是 CPU 与外存之间的关键桥梁,通过内存控制器与 CPU 总线直接连接,承担三大核心功能:

- 存储 CPU 待执行的指令序列

- 暂存运算过程中产生的中间数据

- 缓存外存中频繁访问的数据

其物理构成包括:

- 随机存储器(RAM):占内存主体,如 DDR5 内存条,通过多通道技术提升带宽(如双通道内存带宽 = 单通道 ×2)。

- 只读存储器(ROM):集成于主板,如 CMOS 芯片,存储系统时间、硬件参数等基础配置。

内存性能指标主要包括:容量(如 16GB)、频率(如 3200MHz)、带宽(如 25.6GB/s),直接影响计算机的多任务处理能力和程序运行速度。

高速缓存(Cache):CPU 与内存的速度缓冲

CPU 与内存的速度差距(CPU 纳秒级 vs 内存百纳秒级)是系统性能的主要瓶颈,Cache 通过 “近距离存储高频数据” 解决这一问题 —— 现代 CPU 通常集成三级 Cache:

- L1 Cache:紧连 CPU 核心(如每个核心 32KB),速度最快

- L2 Cache:核心独享(如每个核心 256KB),容量与速度介于 L1 与 L3 之间

- L3 Cache:多核心共享(如 16MB),容量最大

地址映像:主存与 Cache 的映射机制

地址映像是将主存数据块加载到 Cache 的规则,由硬件自动完成,主要方式包括:

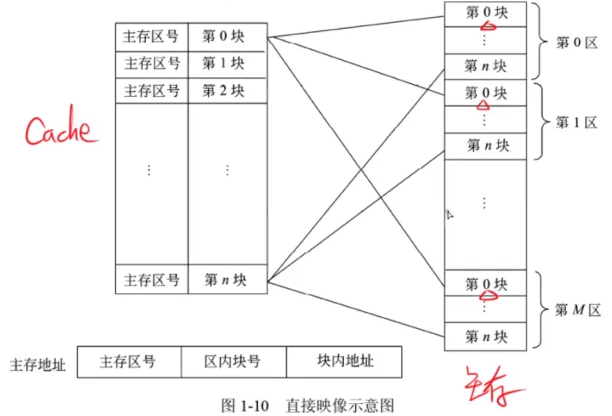

直接相联映像

- 原理:主存按 Cache 大小划分为若干区域,每个区域的块只能对应 Cache 中固定位置(如主存块 i 映射到 Cache 块 i mod Cache 总块数)。

- 特点:硬件简单(仅需模运算),但冲突率最高(不同区域的同序号块会争夺 Cache 位置)。

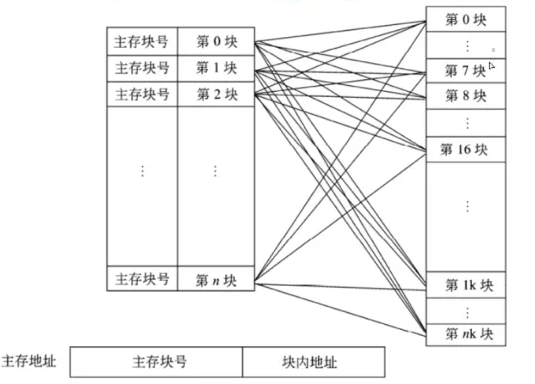

全相联映像

- 原理:主存任意块可映射到 Cache 任意位置,通过相联存储器查找匹配块。

- 特点:冲突率极低,但电路复杂(需比对所有 Cache 块标签),仅适用于小容量 Cache(如 L1)。

组相联映像

- 原理:折中方案,将 Cache 划分为若干组,主存块先映射到固定组(直接相联),再在组内任意放置(全相联)。

- 示例:4 路组相联 Cache 中,主存块先定位到目标组,再在组内 4 个块中选择位置。

- 特点:冲突率低于直接相联,硬件复杂度低于全相联,是主流设计(如 L2、L3 Cache 多采用 8 路组相联)。

替换策略:Cache 满时的数据淘汰规则

当 Cache 空间已满,需按策略淘汰旧数据,常见算法包括:

- 随机算法:随机选择淘汰块,实现简单但效率低。

- 先进先出(FIFO):淘汰最早进入 Cache 的块(用队列记录顺序),未考虑访问频率。

- 最不经常使用(LFU):淘汰访问次数最少的块(需计数器记录频率),适合高频访问场景。

- 最近最少使用(LRU):淘汰最久未被访问的块(用双向链表记录访问时序),符合局部性原理,应用最广泛。

v1.3.10